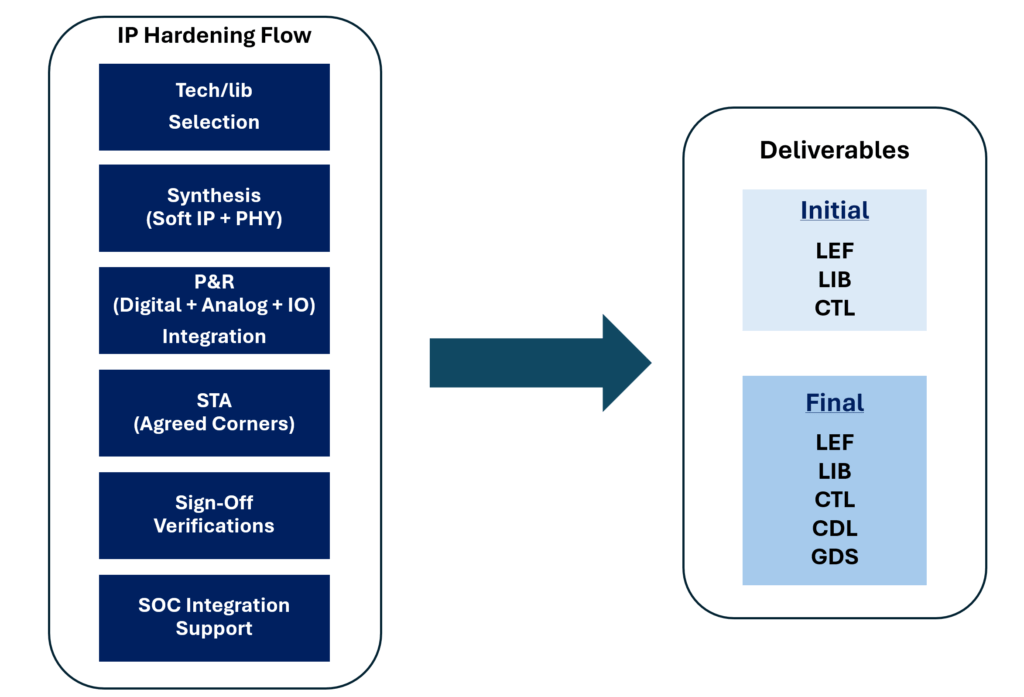

IP Hardening

IP hardening encompasses the integration of the controller module and PHY macro for high-speed IPs such as USB, PCIe, Ethernet, or DDR tailored for the specific technology node. This process involves the synthesis, placement and routing (P&R), static timing analysis (STA), and physical verification (PV) of soft IPs, followed by their integration with the PHY macro. The key benefit of this approach is that the IP is delivered as a single hard macro with all timings finalized, I/O integrated, etc. This makes it ready for seamless, plug-and-play integration into an SoC, streamlining the overall Chip level integration smoother.

Always Ready To Help YOU